## 100BASE-T1 PHY가 통합된 5포트 AVB/TSN 기가비트 이더넷 스위치

#### 주요 내용

- 4개의 100BASE-T1 포트

- 1개의 RGMII/RMII/MII 포트

- 더 많은 포트 수를 위한 캐스케이드 모드

- 향상된 EMC 성능

- 완전한 AVB 오디오 비디오 브리지

- Time Sensitive Networking 지원

- High Available Seamless Redundancy (HSR)

- OPEN Alliance TC10 Sleep/Wakeup

- 과열 및 저전압 감지

- LinkMD®+ 향상된 케이블 진단

- FlexPWR® 기술 전원 관리

- Small-footprint wettable 64-pin VQFN (8 x 8 mm)

- AEC-Q100 오토모티브 제품 인증

- Grade 2 Automotive temperature (-40°C to +105°C)

#### 적용 대상

- ADAS(고급 운전자 보조 시스템)

- 인포테인먼트

- 텔레매틱스 및 스마트 안테나

- 차량 내 백본통신망

- 게이트웨이

#### 기능

- 스위치 관리 기능

- OPEN TC11 스위치 요구 사항 준수

- 1K MAC 테이블

- IEEE 802.1Q VLAN 지원

- AVB 및 TSN 하드웨어 지원:

- -IEEE 802.1AS 시간 동기화

- -IEEE 1588v2 PTP 및 클록 동기화

- -IEEE 802.Qav 트래픽 셰이핑

- -IEEE 802.1Qbv(TSN) 시간 인식 스케줄러

- -IEEE 802.1Qci(TSN) 인그레스 필터링 및 폴리싱

- 포트당 8개의 셰이퍼, 각 대기열당 한 개

- 스마트 저지연 컷스루 포워딩 모드

- HSR(고가용성 무중단 이중화)

- TCAM을 사용한 심층 패킷 검사(DPI) -레이어 2, 3, 4 이상에 대한 TCAM 분류

- SPI 또는 인밴드 호스트 프로세서 액세스

- Wire speed 논블로킹

- 4 x Integrated 100BASE-T1 이더넷 PHY

- IEEE 802.3bw-2015 준수

- single balanced twisted pair cable을 통한 100Mbps

- 15M 이상으로 케이블 길이 연장

- Balanced UTP 케이블에 대한 온칩 필터링 및 종단

- 1개의 구성 가능한 외부 MAC 포트

- RGMII(Reduced Gigabit Media Independent Interface)

- 50MHz 레퍼런스 클록 입력/출력 옵션이 있는 RMII(Reduced Gigabit Media Independent Interface)

- PHY/MAC 모드의 MII(Media Independent Interface)

- IEEE 1588v2 PTP 및 클록 동기화

- Transparent Clock (TC) with auto correction update

- Leader and Follower Ordinary Clock (OC) 지원

- 엔드 투 엔드(E2E) 또는 피어 투 피어(P2P)

- PTP 멀티캐스트 및 유니캐스트 메시지 지원

- IPv4/v6 및 IEEE 802.3을 통한 PTP 메시지 전송

- IEEE 1588v2 PTP 패킷 필터링

- Time Aware Precision GPIO

- 고급 진단 및 보안

- OPEN Alliance(TC1) 고급 진단 준수

- LinkMD®+케이블 진단기능

- -케이블 오픈/단락/길이 결정

- -MSE가 있는 신호 품질 표시기(SQI), 피크 값 및 피크/임계값 인터럽트

- 셀프 테스트 패킷 생성기/감지기

- -단일 버스트 및 연속 트래픽 스트림 지원

- -자동 L2 및 구성 가능한 L3 및 L4 헤더

- 루프백 모드(IEEE 802.3bw 기준)

- 확장된 MIB 성능 카운터

- 모든 패킷/포트에 대한 심층 패킷 검사 지원

- IEEE 802.1AR(802.1x) 포트 및 MAC 인증

- IEEE 802.1Qci 스트림당 인그레스 필터링 및 폴리싱

- EtherGREEN<sup>™</sup> 에너지 효율성

- 저전력 100BASE-T1 PHY 기술

- OPEN Alliance TC10 슬립/복귀(부분 네트워킹)

- non-TC10 링크 파트너 에너지 감지 wake-up 지원

- Ultra-Deep-Sleep power down

- 낮은 RF 방츨

- 통합 전송 필터링

- xMII 데이터 및 125MHz 클록에 프로그래밍 가능한 슬루 레이트 제어 포함

- OPEN Alliance(TC6) RGMII EPL 준수

- OPEN Alliance 트랜시버 EMC 테스트 사양 초과 만족

## 소중한 고객 여러분께

당사는 소중한 고객 여러분이 Microchip 제품을 잘 사용할 수 있도록 최고의 설명서를 제공하려고 합니다. 이를 위해 고객의 필요에 맞춰 계속해서 출판물을 개선합니다. 당사 출판물은 개정, 보완 및 업데이트되어 새롭게 제공될 예정입니다.

본 출판물에 대한 질문이나 의견이 있는 경우 이메일(docerrors@microchip.com)을 통해 Marketing Communications Department로 문의하십시오. 여러분의 의견을 기다리겠습니다.

#### 최신 문서

이 문서의 최신 버전을 받으려면 다음 주소의 당사 전세계 웹 사이트에 등록하십시오.

다음 중 하나를 통해 특정 디바이스에 대한 정오표가 있는지 확인할 수 있습니다.

#### http://www.microchip.com

페이지 하단의 바깥쪽 모서리에 있는 문헌 번호로 데이터 시트의 버전을 확인할 수 있습니다. 문헌 번호의 마지막 문자가 버전 번호입니다. 예를 들어, DS30000000A는 문서 DS30000000의 버전 A입니다.

#### **Errata**

현재 디바이스에 대해 데이터 시트에서 발견된 작업상의 사소한 차이 및 권장 해결 방법을 설명하는 정오표가 있을 수 있습니다. 디 바이스/문서 문제가 파악되면 정오표가 배포됩니다. 여기에는 해당 실리콘 리비전과 문서의 수정 버전이 명시됩니다.

- Microchip의 전세계 웹 사이트: http://www.microchip.com

- 해당 지역의 Microchip 세일즈 오피스(마지막 페이지 참조)

영업소에 문의할 경우 사용 중인 디바이스, 실리콘 리비전 및 데이터 시트(문헌 번호 포함)를 알려주십시오.

#### 고객 알림 시스템

당사의 모든 제품에 대한 최신 정보를 받아보려면 당사 웹 사이트(www.microchip.com)에 등록하십시오.

## 목차

| 1.0 서문                  |    |

|-------------------------|----|

| 2.0 소개                  | 8  |

| 3.0 핀 설명 및 구성           | 10 |

| 4.0 패키지 정보              |    |

| Appendix A: 제품 개요 개정 내역 | 22 |

| <br>Microchip 웹 사이트     | 23 |

| 고객 변경 사항 알림 서비스         | 23 |

| 고객 지원                   | 23 |

| 제품 식별 시스템               | 24 |

## 1.0 서문

## 1.1 일반 용어

## 표 1-1: 일반 용어

| 용어         | 설명                                                                  |  |  |  |

|------------|---------------------------------------------------------------------|--|--|--|

| 1000BASE-T | twisted pair를 통한 1Gbps 이더넷, IEEE 802.3 규격                           |  |  |  |

| 100BASE-T1 | single balanced twisted pair을 통한 100Mbps 이더넷, IEEE 802.3bw 규격       |  |  |  |

| 100BASE-TX | twisted pair를 통한 100Mbps 이더넷, IEEE 802.3 규격                         |  |  |  |

| 10BASE-T   | twisted pair를 통한 10Mbps 이더넷, IEEE 802.3 규격                          |  |  |  |

| ACL        | 액세스 컨트롤 목록(Access Control List)                                     |  |  |  |

| ADAS       | 고급 운전자 보조 시스템(Advanced Driver Assistance System)                    |  |  |  |

| ADC        | 아날로그-디지털 변환기(Analog-to-Digital Converter)                           |  |  |  |

| AFE        | 아날로그 프런트 엔드(Analog Front End)                                       |  |  |  |

| AN, ANEG   | Auto-Negotiation                                                    |  |  |  |

| ARP        | 어드레스 결정 프로토콜(Address Resolution Protocol)                           |  |  |  |

| AVB        | 오디오 비디오 브리지(Audio Video Bridging)                                   |  |  |  |

| BELT       | Best Effort Latency Tolerance                                       |  |  |  |

| BYTE       | 8-bit                                                               |  |  |  |

| CRC        | 순환 중복 검사(Cyclic Redundancy Check)                                   |  |  |  |

| CSMA/CD    | 반송파 감지 다중 액세스/충돌 감지(Carrier Sense Multiple Access/Collision Detect) |  |  |  |

| CSR        | 컨트롤 및 상태 레지스터(Control and Status Register)                          |  |  |  |

| DA         | 목적지 어드레스(Destination Address)                                       |  |  |  |

| DoD        | 목적지에서의 지연(Delay on Destination)                                     |  |  |  |

| DoS        | 소스에서의 지연(Delay on Source)                                           |  |  |  |

| DWORD      | 32-bit                                                              |  |  |  |

| E2E        | 엔드 투 엔드(End to End)                                                 |  |  |  |

| EC         | 임베디드 컨트롤러(Embedded Controller)                                      |  |  |  |

| EEE        | Energy Efficient Ethernet                                           |  |  |  |

| EOF        | 프레임 엔드(End of Frame)                                                |  |  |  |

| FCS        | 프레임 검사 시퀀스(Frame Check Sequence)                                    |  |  |  |

| FID        | 필터 ID(Filter ID)                                                    |  |  |  |

| FIFO       | 선입선출(First In First Out) 버퍼                                         |  |  |  |

| FSM        | Finite State Machine                                                |  |  |  |

| FW         | 펌웨어(Firmware)                                                       |  |  |  |

| GMII       | Gigabit Media Independent Interface                                 |  |  |  |

| GPIO       | 범용 I/O(General Purpose I/O)                                         |  |  |  |

| gPTP       | 범용 정밀 시간 프로토콜(Generic Precision Time Protocol)                      |  |  |  |

| HOST       | 외부 시스템(프로세서, 응용 프로그램 소프트웨어 등 포함)                                    |  |  |  |

## 표 1-1: 일반 용어 (CONTINUED)

| 용어    | 설명                                                                 |  |  |  |  |

|-------|--------------------------------------------------------------------|--|--|--|--|

| HSR   | 고가용성 무중단 이중화(High-availability Seamless Redundancy)                |  |  |  |  |

| HW    | 하드웨어(Hardware). 디지털 논리로 구현되는 기능을 의미함.                              |  |  |  |  |

| IEEE  | 미국 전기전자 학회(Institute of Electrical and Electronic Engineers)       |  |  |  |  |

| IGMP  | 인터넷 그룹 관리 프로토콜(Internet Group Management Protocol)                 |  |  |  |  |

| IP    | 인터넷 프로토콜                                                           |  |  |  |  |

| IPV   | 내부 우선 순위 값(Internal Priority Value)                                |  |  |  |  |

| ISO   | 국제 표준 기구(International Standards Organization)                     |  |  |  |  |

| ITU   | 국제 전기 통신 연합(International Telecommunications Union)                |  |  |  |  |

| L2    | 계층 2(Layer 2)                                                      |  |  |  |  |

| L3    | 계층 3(Layer 3)                                                      |  |  |  |  |

| L4    | 계층 4(Layer 4)                                                      |  |  |  |  |

| LDO   | 선형 드롭 아웃(Linear Drop-Out) 레귤레이터                                    |  |  |  |  |

| LIDAR | 빛을 통한 검출과 거리 측정 (Light Detection and Ranging)                      |  |  |  |  |

| LPM   | 링크 전원 관리(Link Power Management)                                    |  |  |  |  |

| Isb   | 최하위 비트(Least Significant Bit)                                      |  |  |  |  |

| LSB   | 최하위 바이트(Least Significant Byte)                                    |  |  |  |  |

| MAC   | 미디어 액세스 컨트롤러(Media Access Controller)                              |  |  |  |  |

| MDI   | 미디어 종속 인터페이스(Medium Dependent Interface)                           |  |  |  |  |

| MDIX  | 미디어 독립 인터페이스(크로스오버 포함)(Media Independent Interface with Crossover) |  |  |  |  |

| MII   | 미디어 독립 인터페이스(Media Independent Interface)                          |  |  |  |  |

| MSTP  | 다중 스패닝 트리 프로토콜(Multiple Spanning Tree Protocol)                    |  |  |  |  |

| N/A   | 해당 없음(Not Applicable)                                              |  |  |  |  |

| Nonce | 1회만 사용되는 임의 숫자                                                     |  |  |  |  |

| NoQ   | 대기열 수(Number of Queues)                                            |  |  |  |  |

| NumP  | 포트 수(Number of Ports)                                              |  |  |  |  |

| ОС    | Ordinary Clock                                                     |  |  |  |  |

| ОТР   | 1회 프로그램 가능(One Time Programmable)                                  |  |  |  |  |

| P2P   | 피어 투 피어(Peer to Peer)                                              |  |  |  |  |

| PCS   | 물리적 코딩 하위 계층(Physical Coding Sublayer)                             |  |  |  |  |

| PIO   | 프로그래밍 가능 입력 및 출력(Programmable Input and Output)                    |  |  |  |  |

| PLL   | 위상 고정 루프(Phase Locked Loop)                                        |  |  |  |  |

| PMIC  | 전원 관리 IC(Power Management IC)                                      |  |  |  |  |

| POR   | 파워온 리셋(Power on Reset)                                             |  |  |  |  |

| PPS   | 초당 패킷(Packets Per Second)                                          |  |  |  |  |

| PSFP  | 스트림당 필터링 및 폴리싱(Per-Stream Filtering and Policing)                  |  |  |  |  |

## 표 1-1: 일반 용어 (CONTINUED)

| 용어       | 설명                                                                                                                                                                 |  |  |  |  |  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| PTF      | 포워딩할 포트(Port to Forward)                                                                                                                                           |  |  |  |  |  |

| PTP      | 정밀 시간 프로토콜(Precision Time Protocol)                                                                                                                                |  |  |  |  |  |

| QoS      | 서비스 품질(Quality of Service)                                                                                                                                         |  |  |  |  |  |

| QWORD    | 64-bit                                                                                                                                                             |  |  |  |  |  |

| RESERVED | 예약된 비트 필드나 어드레스를 나타냅니다. 다른 설명이 없는 한 예약된 bit는 쓰기<br>작업에 대해 항상 0이어야 합니다. 다른 설명이 없는 한 예약된 bit를 읽을 때 값이 보<br>증되지 않습니다. 다른 설명이 없는 한 예약된 어드레스를 읽거나 예약된 어드레스에<br>쓰지 마십시오. |  |  |  |  |  |

| RGMII    | 감소된 기가비트 미디어 독립 인터페이스(Reduced Gigabit Media Independent Interface)                                                                                                 |  |  |  |  |  |

| RMII     | 감소된 미디어 독립 인터페이스(Reduced Media Independent Interface)                                                                                                              |  |  |  |  |  |

| RMON     | 원격 모니터링(Remote Monitoring)                                                                                                                                         |  |  |  |  |  |

| RTC      | 실시간 클록(Real Time Clock)                                                                                                                                            |  |  |  |  |  |

| SA       | 소스 어드레스(Source Address)                                                                                                                                            |  |  |  |  |  |

| SCSR     | 시스템 컨트롤 및 상태 레지스터(System Control and Status Registers)                                                                                                             |  |  |  |  |  |

| SDU      | 서비스 데이터 단위(Service Data Unit)                                                                                                                                      |  |  |  |  |  |

| SFD      | 프레임 구분 기호의 시작(Start of Frame Delimiter) - 이더넷 프레임의 프리엠블 끝을<br>나타내는 8비트 값입니다.                                                                                       |  |  |  |  |  |

| SNMP     | 단순 네트워크 관리 프로토콜(Simple Network Management Protocol)                                                                                                                |  |  |  |  |  |

| SOF      | 프레임 시작(Start of Frame)                                                                                                                                             |  |  |  |  |  |

| STC      | System Time Clock                                                                                                                                                  |  |  |  |  |  |

| TA       | 반송 시간(Turn-Around Time)                                                                                                                                            |  |  |  |  |  |

| TAS      | 시간 인식 스케줄러(Time Aware Scheduler)                                                                                                                                   |  |  |  |  |  |

| TC       | 투명 시계(Transparent Clock)                                                                                                                                           |  |  |  |  |  |

| ТСР      | 컨트롤 프로토콜 전송(Transport Control Protocol)                                                                                                                            |  |  |  |  |  |

| TMII     | 터보 미디어 독립 인터페이스(Turbo Media Independent Interface)                                                                                                                 |  |  |  |  |  |

| UDP      | 사용자 데이터그램 프로토콜(User Datagram Protocol) - IP 네트워크 상위에서 실행<br>되는 연결이 없는 프로토콜                                                                                         |  |  |  |  |  |

| UTP      | 비차폐 연선(Unshielded Twisted Pair)                                                                                                                                    |  |  |  |  |  |

| VLAN     | Virtual Local Area Network                                                                                                                                         |  |  |  |  |  |

| WORD     | 16-bit                                                                                                                                                             |  |  |  |  |  |

### 1.2 버퍼 유형

#### 표 1-2: 버퍼 유형

| 버퍼 유형    | 설명                                                                                                                                                                     |  |  |  |  |  |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| VIS      | 가변 슈미트 트리거 입력                                                                                                                                                          |  |  |  |  |  |

| VIS_VBAT | VBAT 전원 도메인의 가변 슈미트 트리거 입력                                                                                                                                             |  |  |  |  |  |

| IPU      | 내부 풀업이 있는 입력(58kΩ ±30%)                                                                                                                                                |  |  |  |  |  |

| VO8      | 8mA 싱크 및 8mA 소스가 있는 가변 출력                                                                                                                                              |  |  |  |  |  |

| VO_VBAT  | VBAT 전원 도메인의 가변 출력                                                                                                                                                     |  |  |  |  |  |

| Α        | 아날로그                                                                                                                                                                   |  |  |  |  |  |

| ICLK     | 크리스털 오실레이터 입력 핀                                                                                                                                                        |  |  |  |  |  |

| OCLK     | 크리스털 오실레이터 출력 핀                                                                                                                                                        |  |  |  |  |  |

| Р        | 전원                                                                                                                                                                     |  |  |  |  |  |

| OD       | 오픈 드레인 출력                                                                                                                                                              |  |  |  |  |  |

| RGMII    | RGMII 출력                                                                                                                                                               |  |  |  |  |  |

| PU       | 70K(일반) 내부 풀업. 핀 설명에 다르게 명시되지 않는 한 내부 풀업은 항상 활성화됩니다.  Note: 내부 풀업 저항이 연결되지 않은 입력의 플로팅을 방지합니다. 내부 저항을 사용하여 디바이스 외부의 신호를 구동하지 마십시오. 높은 풀업이 필요한 로드에 연결되면 외부 저항을 추가해야 합니다. |  |  |  |  |  |

Note: 전원 켜기/핀 리셋 중에는 모든 디지털 입력 핀에 의해 내부 풀업이 활성화됩니다.

## 1.3 참조 문서

- 1. IEEE 802.3<sup>TM</sup>-2015 IEEE 이터넷 표준 http://standards.ieee.org/about/get/802/802.3.html

- 2. *IEEE 802.3bw<sup>TM</sup>-2015 IEEE 이더넷 표준 수정판 1* https://standards.ieee.org/findstds/standard/802.3bw-2015.html

- 3. RMII 사양 개정판 1.2 http://ebook.pldworld.com/\_eBook/-Telecommunications,Networks-/TCPIP/RMII/rmii\_rev12.pdf

- 4. RGMII(Reduced Gigabit Media Independent Interface) 사양 버전 2.0 https://web.archive.org/web/20160303171328/http://www.hp.com/rnd/pdfs/RGMIIv2\_0\_final\_hp.pdf

- 5. OPEN Alliance TC1 100BASE-T1 자동차 이더넷 PHY용 고급 진단 기능 버전 1.0 http://www.opensig.org//about/specifications/

- 6. OPEN Alliance TC10 슬립/복귀 사양 버전 2.0 http://www.opensig.org//about/specifications/

#### 2.0 소개

### 2.1 일반설명

Microchip LAN9370은 IEEE 802.3bw-2015 사양을 기반으로 한 확장 가능하고 컴팩트하며 비용 효율적인 멀티 포트 AVB/TSN 100BASE-T1 이더넷 스위치입니다. LAN9370은 layer 2 이상의 고성능 managed 이더넷 스치와 4개의 100BASE-T1 PHY(물리적 계층 트랜시버) 및 구성 가능한 RGMII/MII/RMII 인터페이스 1개를 갖는 1개의 MAC 포트를 통합하여 호스트 프로세서/컨트롤러, 또 다른 이더넷 스위치 또는 이더넷 PHY 트랜시버에 직접 연결할 수 있습니다. LAN9370은 Grade 2 Automotive (-40°C ~ +105°C) 온도 사양을 충족하며 게이트 웨이, ADAS(자동화된 운전자 보조 시스템), 인포테인먼트, 텔레매틱스 및 차량 내 네트워킹과 같은 AEC-Q100 오토모티브 사용 사례에 적합합니다.

LAN9370은 이더넷을 통해 전송되는 지연 시간에 민감한 트래픽 스트림을 위해 높은 QoS(Quality of Service)를 제공하는 AVB(Audio Video Bridging) 표준인 IEEE 패밀리를 완전히 지원합니다. 하드웨어 타임스탬프 및 시간 기록 기능을 통해 IEEE 802.1AS(gPTP) 및 IEEE 1588v2(PTP) 시간 동기화를 지원합니다. 모든 포트에는 IEEE 802.1Qbv 사양에 따라 8개의 송신 대기열과 IEEE 802.1Qav 크레딧 기반 트래픽 쉐이퍼 및 시간 인식 스케줄러가 탑재되어 있습니다.

호스트 프로세서는 모든 LAN9370 레지스터에 액세스하여 모든 PHY, MAC 및 스위치 기능을 제어할 수 있습니다. 통합되어 있는 SMI 및 SPI 인터페이스를 통해 그리고 데이터 포트 중 어느 하나를 통한 인밴드 매니지먼트로 전체 레지스터에 액세스할 수 있습니다. PHY 레지스터 액세스는 MIIM 인터페이스를 통해 제공됩니다. 유연한 디지털 I/O 전압을 통해 MAC 포트에서 1.8/2.5/3.3V 호스트 프로세서/컨트롤러/FPGA로 직접 인터페이스할 수 있습니다.

또한 Open Alliance TC10 Sleep/Wake-up 부분 네트워킹, non-TC10 링크 파트너 에너지 감지 복귀, 완전 절전 전원 끄기 기능을 포함한 강력한 EtherGREEN<sup>TM</sup> 에너지 효율성 기능 모음이 제공됩니다.

표 2-1에는 LAN937x 디바이스 제품군 모델 간 기능 차이가 요약되어 있습니다.

표 2-1: LAN937X 제품군 기능 매트릭스

| 나<br>문<br>나 | 파키지      | 내부 100BASE-T1 PHY<br>개수 | 100BASE-TX<br>지원 | SGMII 지원 | RGMII/RMII/MII<br>포트 | 완전한 AVB 지원 | 시간에 민감한<br>네트워킹 지원 | OPEN Alliance<br>TC10 슬립/복귀<br>에너지 효율성 | 캐스케이드 모드<br>지원 | AEC-Q100<br>인증 | 2등급<br>자동차 온도<br>(-40° ~ 105°C) |

|-------------|----------|-------------------------|------------------|----------|----------------------|------------|--------------------|----------------------------------------|----------------|----------------|---------------------------------|

| LAN9370     | 64-VQFN  | 4                       |                  |          | 1                    | Х          | X                  | Х                                      | X              | Х              | Х                               |

| LAN9371     | 128-TQFP | 3                       | Х                |          | 2                    | Х          | Х                  | Х                                      | Х              | Х              | Х                               |

| LAN9372     | 128-TQFP | 5                       | Х                |          | 2                    | Х          | Х                  | Х                                      | Х              | Х              | Х                               |

| LAN9373     | 128-TQFP | 5                       |                  | Х        | 2                    | Х          | Х                  | Х                                      | Х              | Х              | Х                               |

| LAN9374     | 128-TQFP | 6                       |                  |          | 2                    | X          | Х                  | Х                                      | X              | Х              | Х                               |

Note: 모든 LAN937x 디바이스는 하나의 공통 소프트웨어 드라이버를 공유합니다. 모든 128-TQFP LAN937x 디바이스는 핀 호환성을 가집니다.

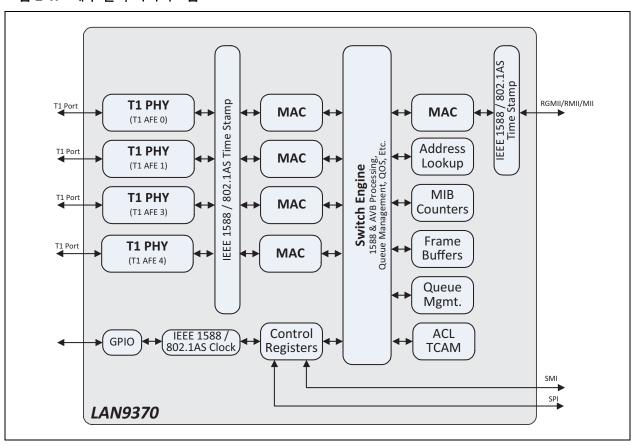

LAN9370의 내부 블록 다이어그램이 그림 2-1에 나와 있습니다.

## 그림 2-1: 내부 블록 다이어그램

- 3.0 핀 설명 및 구성

- 3.1 핀 할당

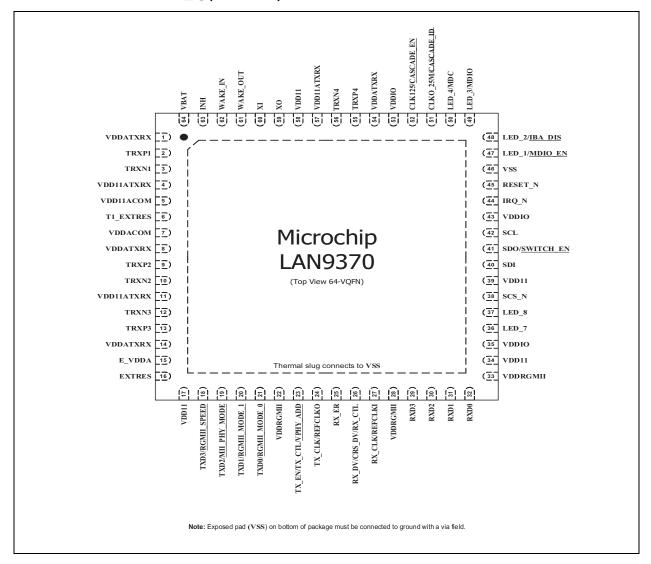

그림 3-1: LAN9370 핀 할당(TOP VIEW)

표 3-1: LAN9370 핀 할당

| 핀       | 핀 이름                   | 핀  | 핀 이름            | 핀  | 핀 이름      | 핀  | 핀 이름       |

|---------|------------------------|----|-----------------|----|-----------|----|------------|

| 1       | VDDATXRX               | 17 | VDD11           | 33 | VDDRGMII  | 49 | LED_3/MDIO |

| 2       | TRXP1                  | 18 | TXD3/           | 34 | VDD11     | 50 | LED_4/MDC  |

|         |                        |    | RGMII_SPEED     |    |           |    |            |

| 3       | TRXN1                  | 19 | TXD2/           | 35 | VDDIO     | 51 | CLKO_25M/  |

|         |                        |    | MII_PHY_MODE    |    |           |    | CASCADE_ID |

| 4       | VDD11ATXRX             | 20 | TXD1/           | 36 | LED_7     | 52 | CLK125/    |

|         |                        |    | RGMII_MODE_1    |    |           |    | CASCADE_EN |

| 5       | VDD11ACOM              | 21 | TXD0/           | 37 | LED_8     | 53 | VDDIO      |

|         |                        |    | RGMII_MODE_0    |    |           |    |            |

| 6       | T1_EXTRES              | 22 | VDDRGMII        | 38 | SCS_N     | 54 | VDDATXRX   |

| 7       | VDDACOM                | 23 | TX_EN/TX_CTL/   | 39 | VDD11     | 55 | TRXP4      |

|         |                        |    | <u>VPHY_ADD</u> |    |           |    |            |

| 8       | VDDATXRX               | 24 | TX_CLK/REFCLKO  | 40 | SDI       | 56 | TRXN4      |

| 9       | TRXP2                  | 25 | RX_ER           | 41 | SDO/      | 57 | VDD11ATXRX |

|         |                        |    |                 |    | SWITCH_EN |    |            |

| 10      | TRXN2                  | 26 | RX_DV/CRS_DV/   | 42 | SCL       | 58 | VDD11      |

|         |                        |    | RX_CTL          |    |           |    |            |

| 11      | VDD11ATXRX             | 27 | RX_CLK/REFCLKI  | 43 | VDDIO     | 59 | XO         |

| 12      | TRXN3                  | 28 | VDDRGMII        | 44 | IRQ_N     | 60 | XI         |

| 13      | TRXP3                  | 29 | RXD3            | 45 | RESET_N   | 61 | WAKE_OUT   |

| 14      | VDDATXRX               | 30 | RXD2            | 46 | VSS       | 62 | WAKE_IN    |

| 15      | E_VDDA                 | 31 | RXD1            | 47 | LED_1/    | 63 | INH        |

|         |                        |    |                 |    | MDIO_EN   |    |            |

| 16      | EXTRES                 | 32 | RXD0            | 48 | LED_2/    | 64 | VBAT       |

| IBA_DIS |                        |    |                 |    |           |    |            |

|         | 노출된 패드는 VSS에 연결해야 합니다. |    |                 |    |           |    |            |

$\ensuremath{\texttt{©}}$  2023 Microchip Technology Inc.

## 3.2 핀 설명

이 섹션에서는 다양한 LAN9370 핀에 대한 설명을 다룹니다. 버퍼 유형 정의는 섹션 1.2, "버퍼 유형"에 자세히 설명되어 있습니다.

신호 이름의 "\_N" 기호는 신호가 낮은 전압 레벨에 있을 때 활성 또는 인가된 상태가 발생함을 나타냅니다. 예를 들어,  $RESET_N$ 은 리셋 신호가 활성 낮음 상태임을 나타냅니다. 신호 이름 뒤에 "\_N"이 없으면 신호는 높은 전압 레벨에서 인가됩니다.

구성 스트랩을 사용하면 디바이스의 다양한 기능을 사용자 정의된 값으로 자동 구성할 수 있습니다. 구성 스트랩은 밑줄로 된 기호 이름으로 식별되며 파워온 리셋(POR) 및 핀 리셋(RESET\_N) 시에 래치됩니다. 구성 스트랩에는 내부 풀업/풀다운 저항이 포함되어 있어 연결되지 않은 경우 신호의 부동을 방지합니다.

Note: 구성 스트랩으로 기능을 하는 신호는 래칭 전에 필요한 전압 레벨에 도달하도록 부하 연결 시 외부 풀업 또는 풀다운 저항으로 보강되어야 합니다.

#### 표 3-2: 핀 설명

| 이름                                      | 기호                    | 버퍼 유형   | 설명                                                                                     |  |  |  |  |  |  |

|-----------------------------------------|-----------------------|---------|----------------------------------------------------------------------------------------|--|--|--|--|--|--|

|                                         | 100BASE-T1 이더넷 PHY 포트 |         |                                                                                        |  |  |  |  |  |  |

| 포트 4-1<br>100BASE-T1<br>PHY TX/RX<br>양극 | TRXP[4:1]             | A       | 포트 4-1 100BASE-T1 PHY 송신/수신 양극                                                         |  |  |  |  |  |  |

| 포트 4-1<br>100BASE-T1<br>PHY TX/RX<br>음극 | TRXN[4:1]             | A       | 포트 4-1 100BASE-T1 PHY 송신/수신 음극                                                         |  |  |  |  |  |  |

| 100BASE-T1<br>참조 저항                     | T1_EXTRES             | А       | T1 PHY 공통 블록에 대한 레퍼런스 저항 연결 핀 올바른<br>작동을 위해 이 핀을 6.49kΩ 0.1% 저항을 통해 VSS에 연<br>결해야 합니다. |  |  |  |  |  |  |

| 참조 저항                                   | EXTRES                | А       | 참조 저항 연결 핀. 올바른 작동을 위해 이 핀을 $6.49k\Omega$ +/- $0.1\%$ 저항을 통해 $VSS$ 에 연결해야 합니다.         |  |  |  |  |  |  |

|                                         |                       | RGMII/R | RMII/MII 포트                                                                            |  |  |  |  |  |  |

| RGMII/RMII/MII<br>송신                    | TXD3                  | RGMII   | MII/RGMII 모드: 송신 데이터 버스 비트 3 출력                                                        |  |  |  |  |  |  |

| 데이터 3                                   |                       |         | RMII 모드: 사용 안 함                                                                        |  |  |  |  |  |  |

|                                         |                       |         | Note: 이 핀은 또한 하드웨어/소프트웨어 리셋 중에<br>구성 스트랩 기능을 제공합니다.                                    |  |  |  |  |  |  |

| RGMII/RMII/MII<br>송신                    | TXD2                  | RGMII   | MII/RGMII 모드: 송신 데이터 버스 비트 2 출력                                                        |  |  |  |  |  |  |

| 데이터 2                                   |                       |         | RMII 모드: 사용 안 함                                                                        |  |  |  |  |  |  |

|                                         |                       |         | Note: 이 핀은 또한 하드웨어 리셋 중에 구성 스트랩<br>기능을 제공합니다.                                          |  |  |  |  |  |  |

| RGMII/RMII/MII                          | TXD1                  | RGMII   | MII/RMII/RGMII 모드: 송신 데이터 버스 비트 1 출력                                                   |  |  |  |  |  |  |

| 송신<br>데이터 1                             |                       |         | Note: 이 핀은 또한 하드웨어 리셋 중에 구성 스트랩<br>기능을 제공합니다.                                          |  |  |  |  |  |  |

| 이름                             | 기호                 | 버퍼 유형 | 설명                                                                                           |

|--------------------------------|--------------------|-------|----------------------------------------------------------------------------------------------|

| RGMII/RMII/MII                 | TXD0               | RGMII | MII/RMII/RGMII 모드: 송신 데이터 버스 비트 0 출력                                                         |

| 송신<br>데이터 0                    |                    |       | Note: 이 핀은 또한 하드웨어 리셋 중에 구성 스트랩<br>기능을 제공합니다.                                                |

| RGMII/RMII/MII<br>송신/<br>참조 클록 | TX_CLK/<br>REFCLKO | RGMII | MII 모드: TX_CLK은 25/2.5MHz 송신 클록입니다. PHY<br>모드에서 이 핀은 출력이고 MAC 모드에서는 입력입니다.                   |

|                                |                    |       | RMII 모드: REFCLKO는 RMII 클록 모드에 있을 때<br>50MHz 레퍼런스 클록 출력입니다. 이 핀을 RMII 일반 모<br>드에서는 사용되지 않습니다. |

|                                |                    |       | <b>RGMII 모드:</b> TX_CLK은 125/25/2.5MHz 송신 클록 출력입니다.                                          |

|                                |                    |       | Note: 이 핀은 또한 하드웨어 리셋 중에 구성 스트랩<br>기능을 제공합니다.                                                |

| RGMII/RMII/MII<br>송신 활성화/      | TX_EN/<br>TX_CTL   | RGMII | MII/RMII 모드: TX_EN은 송신 활성화 출력입니다.                                                            |

| 컨트롤                            | 515_0 515          |       | RGMII 모드: TX_CTL은 송신 컨트롤 출력입니다.                                                              |

|                                |                    |       | Note: 이 핀은 또한 하드웨어 리셋 중에 구성 스트랩<br>기능을 제공합니다.                                                |

| RGMII/RMII/MII<br>수신           | RXD3               | RGMII | MII/RGMII 모드: 수신 데이터 버스 비트 3 입력                                                              |

| 데이터 3                          |                    |       | RMII 모드: 사용 안 함 이 작동 모드에서는 이 핀에 연결하지 마십시오.                                                   |

| RGMII/RMII/MII<br>수신           | RXD2               | RGMII | MII/RGMII 모드: 수신 데이터 버스 비트 2 입력                                                              |

| 데이터 2                          |                    |       | RMII 모드: 사용 안 함 이 작동 모드에서는 이 핀에 연결하지 마십시오.                                                   |

| RGMII/RMII/MII<br>수신<br>데이터 1  | RXD1               | RGMII | MII/RMII/RGMII 모드: 수신 데이터 버스 비트 1 입력                                                         |

| RGMII/RMII/MII<br>수신<br>데이터 0  | RXD0               | RGMII | MII/RMII/RGMII 모드: 수신 데이터 버스 비트 0 입력                                                         |

| RGMII/RMII/MII<br>수신 클록        | RX_CLK/<br>REFCLKI | RGMII | MII 모드: RX_CLK은 25/2.5MHz 수신 클록입니다. PHY<br>모드에서 이 핀은 출력이고 MAC 모드에서는 입력입니다.                   |

|                                |                    |       | RMII 모드: REFCLKI은 RMII 일반 모드에 있을 때 50MHz<br>레퍼런스 클록 입력. 이 핀은 RMII 클록 모드에서는 사용되<br>지 않습니다.    |

|                                |                    |       | <b>RGMII 모드: RX_</b> CLK은 125/25/2.5MHz 수신 클록 출력<br>입니다.                                     |

| 이름                                                       | 기호                          | 버퍼 유형   | 설명                                                                                                                |

|----------------------------------------------------------|-----------------------------|---------|-------------------------------------------------------------------------------------------------------------------|

| · H<br>RGMII/RMII/MII<br>수신<br>데이터 유효/<br>반송파 감지/<br>컨트롤 | RX_DV/<br>CRS_DV/<br>RX_CTL | RGMII   | MII 모드: RX_DV은 수신 데이터 유효/반송파 감지 입력입니다.  RMII 모드: CRS_DV은 반송파 감지/수신 데이터 유효 입력입니다.  RGMII 모드: RX_CTL은 수신 컨트롤 입력입니다. |

| RGMII/RMII/MII<br>수신 오류                                  | RX_ER                       | RGMII   | MII/RMII 모드: 수신 오류 입력  RGMII 모드: 사용 안 함 이 작동 모드에서는 이 핀에 연결하지 마십시오.                                                |

| RGMII/RMII/MII<br>125MHz<br>참조 클록 출력                     | CLK125                      | RGMII   | SoC MAC에 대한 125MHz RGMII 참조 클록 출력  Note: 이 핀은 또한 하드웨어 리셋 중에 구성 스트랩기능을 제공합니다.                                      |

|                                                          |                             | S       | PI 핀                                                                                                              |

| SPI 클록                                                   | SCL                         | VIS     | SPI 클록.<br>지원되는 최대 SPI 클록 주파수는 50MHz입니다.                                                                          |

| SPI<br>칩 선택                                              | SCS_N                       | VIS     | 액티브 로우 SPI 칩 선택 입력                                                                                                |

| SPI 데이터<br>출력                                            | SDO                         | VO8     | SPI 출력 데이터. Note: 이 핀은 또한 하드웨어 리셋 중에 구성 스트랩기능을 제공합니다.                                                             |

| SPI 데이터<br>입력                                            | SDI                         | VIS     | SPI 입력 데이터.                                                                                                       |

|                                                          |                             | МІ      | DIO 핀                                                                                                             |

| SMI 데이터<br>입력/출력                                         | MDIO                        | VIS/VO8 | 직렬 관리 인터페이스 데이터 입력/출력<br>이 핀은 LED_3과 멀티플렉싱됩니다. 이 핀 기능은<br>MDIO_EN 구성 스트랩을 통해 선택됩니다.                               |

| SMI 클록                                                   | MDC                         | VIS     | 직렬 관리 인터페이스 클록<br>이 핀은 LED_4와 멀티플렉싱됩니다. 이 핀 기능은<br>MDIO_EN 구성 스트랩을 통해 선택됩니다.                                      |

| 이름        | 기호      | 버퍼 유형    | 설명                                                                                                      |  |  |  |

|-----------|---------|----------|---------------------------------------------------------------------------------------------------------|--|--|--|

| LED 핀     |         |          |                                                                                                         |  |  |  |

| LED 표시기 1 | LED_1   | VIS/VO8  | LED 표시기 1                                                                                               |  |  |  |

|           |         |          | 이 핀은 또한 프로그래밍 가능한 입력/출력으로도 기능할<br>수 있습니다.                                                               |  |  |  |

|           |         |          | 이 신호는 IEEE 1588 이벤트 트리거 또는 타임스탬프 캡처<br>장치에서 사용하기 위한 입력 또는 출력으로도 사용할 수<br>있습니다. 내부 IEEE 1588 클록과 동기화됩니다. |  |  |  |

|           |         |          | Note: 이 핀은 또한 하드웨어 리셋 중에 구성 스트랩기능을 제공합니다.                                                               |  |  |  |

| LED 표시기 2 | LED_2   | VIS/VO8  | LED 표시기 2                                                                                               |  |  |  |

|           |         |          | 이 핀은 또한 프로그래밍 가능한 입력/출력으로도 기능할<br>수 있습니다.                                                               |  |  |  |

|           |         |          | Note: 이 핀은 또한 하드웨어 리셋 중에 구성 스트랩<br>기능을 제공합니다.                                                           |  |  |  |

| LED 표시기 3 | LED_3   | VIS/VO8  | LED 표시기 3                                                                                               |  |  |  |

|           |         |          | 이 핀은 또한 프로그래밍 가능한 입력/출력으로도 기능할<br>수 있습니다.                                                               |  |  |  |

| LED 표시기 4 | LED_4   | VIS/VO8  | LED 표시기 4                                                                                               |  |  |  |

|           |         |          | 이 핀은 또한 프로그래밍 가능한 입력/출력으로도 기능할<br>수 있습니다.                                                               |  |  |  |

| LED 표시기 7 | LED_7   | VIS/VO8  | LED 표시기 7                                                                                               |  |  |  |

|           |         |          | 이 핀은 또한 프로그래밍 가능한 입력/출력으로도 기능할<br>수 있습니다.                                                               |  |  |  |

| LED 표시기 8 | LED_8   | VIS/VO8  | LED 표시기 8                                                                                               |  |  |  |

|           |         |          | 이 핀은 또한 프로그래밍 가능한 입력/출력으로도 기능할<br>수 있습니다.                                                               |  |  |  |

|           |         | 7        | 타 핀                                                                                                     |  |  |  |

| 시스템 리셋    | RESET_N | VIS      | 시스템 리셋입니다. 이 핀은 액티브 로우입니다.                                                                              |  |  |  |

|           |         |          | Note: 사용하지 않을 경우 이 핀은 VDDIO로 풀업되<br>어야 합니다.                                                             |  |  |  |

| 복귀 입력     | WAKE_IN | VIS_VBAT | Wakeup 입력. Sleep에서 빠져나오기 위해 인가됩니다. 이<br>핀은 OABR TC10 사양에 설명된 wake 입력 옵션을 구현<br>합니다.                     |  |  |  |

|           |         |          | Note: 이 핀은 VBAT 도메인 외부에서 작동합니다.                                                                         |  |  |  |

| 이름                                    | 기호                      | 버퍼 유형      | 설명                                                                                                                       |

|---------------------------------------|-------------------------|------------|--------------------------------------------------------------------------------------------------------------------------|

| 복귀 출력                                 | WAKE_OUT                | VO_VBAT    | Wake 출력. 해당 부품이 sleep에서 벗어날 때 인가됩니다.<br>이 핀은 OABR TC10 사양에 설명된 wake 출력 옵션을 구<br>현합니다.<br>Note: 이 핀은 VBAT 도메인 외부에서 작동합니다. |

| 억제                                    | INH                     | VO_VBAT    | 금지 외부 주 전원 공급 장치를 켜고 끌 때 사용합니다. 이                                                                                        |

| 7.4                                   | 12 (12                  |            | 핀은 오픈 소스 또는 오픈 드레인으로 구성할 수 있습니다.                                                                                         |

|                                       |                         |            | Note: 오픈 소스로 구성하는 경우 외부 풀다운이 필요합니다. 오픈 드레인으로 구성된 경우 이 핀은 외부 풀업을 통해 VBAT에 연결되어야 합니다.                                      |

|                                       |                         |            | Note: RESET_N 인가는 이 핀의 상태에 영향을 미치<br>지 않습니다.                                                                             |

| 인터럽트                                  | IRQ_N                   | VOD        | 액티브 로우, 오픈 드레인 디바이스 인터럽트                                                                                                 |

|                                       |                         |            | Note: 사용하지 않을 경우 핀을 연결하지 않은 상태로<br>두십시오.                                                                                 |

| 25MHz<br>참조 클록                        | CLKO_25M/<br>CASCADE_ID | VO8        | 25MHz 레퍼런스 클록 출력                                                                                                         |

| 크리스털 클록<br>/오실레이터<br>입력               | XI                      | ICLK       | 25MHz 크리스털 클록/오실레이터 입력<br>크리스털을 사용하는 경우 이 입력을 크리스털의 한 리드<br>에 연결해야 합니다. 오실레이터를 사용하는 경우 이 핀은<br>오실레이터에서 온 입력이 됩니다.        |

| 크리스털 클록<br>출력                         | XO                      | OCLK       | 25MHz 크리스털 클록 출력<br>크리스털을 사용하는 경우 이 출력을 크리스털의 한 리드<br>에 연결해야 합니다. 오실레이터를 사용하는 경우 이 핀은<br>연결하지 않은 상태로 둡니다                 |

|                                       | I/O 전                   | 년원 핀, 코어 7 | 전원 핀 및 그라운드 핀                                                                                                            |

| +1.8 ~ 3.3V<br>I/O 전원 공급<br>장치 입력     | VDDIO                   | Р          | IO용 +1.8 ~ 3.3V 가변 전원 공급                                                                                                 |

| +1.1V 디지털<br>코어전원공급<br>장치 입력          | VDD11                   | Р          | +1.1V 디지털 코어 전원                                                                                                          |

| +1.1V T1 공통<br>블록 전원 공급               | VDD11ACOM               | Р          | T1 공통 블록용 +1.1V 아날로그 전원 공급                                                                                               |

| +1.1V<br>TX/RX<br>아날로그 전원<br>공급       | VDD11ATXRX              | Р          | T1 PHY용 +1.1V 아날로그 전원 공급                                                                                                 |

| +2.5 ~ 3.3V<br>TX/RX<br>아날로그 전원<br>공급 | VDDATXRX                | Р          | T1 PHY용 +2.5 ~ 3.3V 아날로그 전원 공급                                                                                           |

| +2.5 ~ 3.3V<br>T1 공통 블록<br>전원 공급      | VDDACOM                 | Р          | T1 공통 블록용 +2.5 ~ 3.3V 아날로그 전원 공급                                                                                         |

| 이름                                             | 기호       | 버퍼 유형 | 설명                                            |

|------------------------------------------------|----------|-------|-----------------------------------------------|

| +2.5 ~ 3.3V<br>VBAT 전원<br>공급                   | VBAT     | Р     | VBAT 도메인용 +2.5 ~ 3.3V 전원 공급                   |

| +1.8 ~ 3.3V<br>RGMII/RMII/MII<br>아날로그 전원<br>공급 | VDDRGMII | Р     | RGMII/MII/RMII 인터페이스용 +1.8 ~ 3.3V 가변 전원<br>공급 |

| +1.1V PLL<br>전원                                | E_VDDA   | Р     | +1.1V PLL 디지털 전원 공급                           |

| 접지                                             | VSS      | Р     | 그라운드 패드                                       |

## 4.0 패키지 정보

## 4.1 패키지 표시 정보

#### 64-VQFN

LAN9370 Rnnn ©3 VCOO YYWWNNN

범례: R 제품리비젼

nnn 내부코드

e3 무광택 주석(Sn) 사용을 나타내는 무연 JEDEC® 마크

V

플랜트 조립

COO

원산지

YY 연도 코드(해당 연도의 마지막 두자리 숫자)

WW 주 코드(1월 첫째 주의 경우 '01' 주)

NNN 영숫자 추적용 코드

Note: 전체 Microchip 부품 번호를 한 라인 안에 모두 표기할 수 없는 경우 다음 라

인으로 넘어가게 되며, 이 경우 고객별 정보에 사용 가능한 문자 수가 제한될

수 있습니다.

\* 표준 디바이스 표기는 Microchip 부품 번호, 연도 코드, 주 코드 및 추적 코드로 구성됩니다. 이를 초과하는 디바이스 표기 시에는 일정 금액이 추가됩니다. 자세한 정보는 Microchip 영업소에 확인하십시오. QTP 디바이스의 경우 특별 표기에 대한 추가 금액은 QTP 금액에 포함되어 있습니다.

## 4.2 패키지 도면

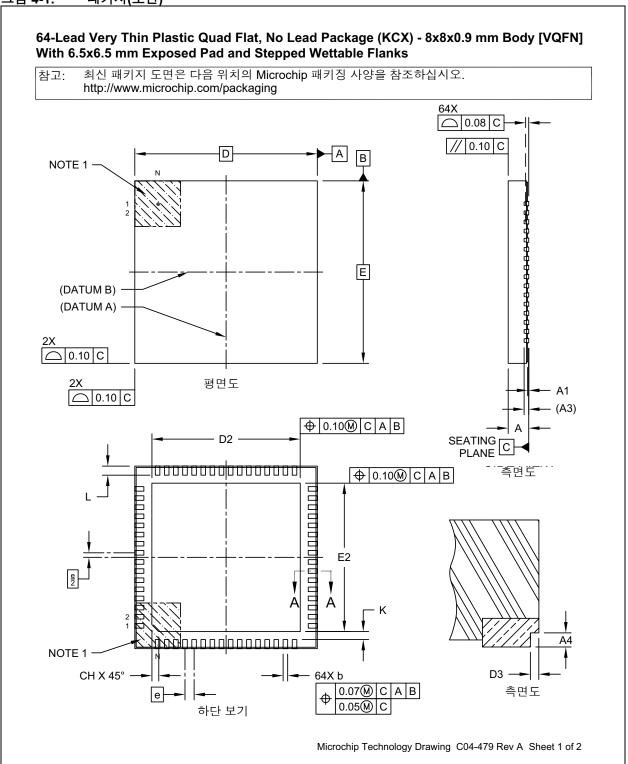

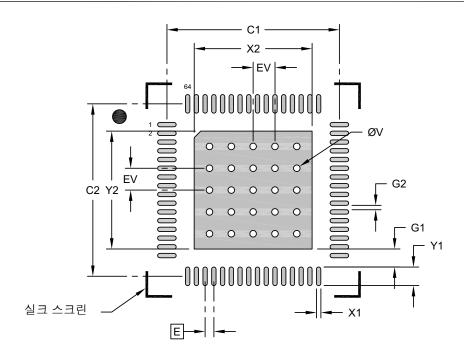

그림 4-1: 패키지(도면)

## 그림 4-2: 패키지(치수)

## 64-Lead Very Thin Plastic Quad Flat, No Lead Package (KCX) - 8x8x0.9 mm Body [VQFN] With 6.5x6.5 mm Exposed Pad and Stepped Wettable Flanks

참고: 최신 패키지 도면은 다음 위치의 Microchip 패키징 사양을 참조하십시오. nttp://www.microchip.com/packaging

| 단위              |      | 밀리미터 |           |       |

|-----------------|------|------|-----------|-------|

| 치               | 수 한계 | MIN  | NOM       | MAX   |

| 터미널 수 N         |      | 64   |           |       |

| 피치              | е    |      | 0.40 BSC  |       |

| 전체 높이           | Α    | -    | -         | 0.90  |

| 스탠드오프           | A1   | 0.00 | 0.02      | 0.05  |

| 터미널 두께          | A3   |      | 0.203 REF |       |

| 전체 길이           | D    |      | 8.00 BSC  |       |

| 노출형 패드 길이 _     | D2   | 6.40 | 6.50      | 6.60  |

| 전체 너비           | Е    |      | 8.00 BSC  |       |

| 노출 패드 너비        | E2   | 6.40 | 6.50      | 6.60  |

| 터미널 너비          | b    | 0.15 | 0.20      | 0.25  |

| 터미널 길이 _        | L    | 0.30 | 0.40      | 0.50  |

| 터미널에서 노출형 패드 연결 | K    | 0.20 | -         | -     |

| 스텝 높이           | A4   | 0.10 | _         | 0.19  |

| 스텝 길이           | D3   | -    | _         | 0.085 |

| 인덱스 코너 챔퍼       | CH   | -    | 0.30      | -     |

#### 참고:

- 1. 핀1 시각적 인덱스 기능은 다양하지만 해치 영역 내에 위치해야 합니다.

- 2. 패키지는 소우 싱귤레이트되어 있음

- 3. 치수 및 공차는 ASME Y14.5M 참조

BSC: 기준 치수입니다. 공차를 제외하고 이론적으로 정확한 값으로 표시되었습니다.

REF: 참고 치수의 약자로서 일반적으로 공차가 없으며 정보 목적으로만 사용합니다.

Microchip Technology Drawing C04-479 Rev A Sheet 1 of 2

## 그림 4-3: 패키지(랜드 패턴)

# 64-Lead Very Thin Plastic Quad Flat, No Lead Package (KCX) - 8x8x0.9 mm Body [VQFN] With 6.5x6.5 mm Exposed Pad and Stepped Wettable Flanks

참고: 최신 패키지 도면은 다음 위치의 Microchip 패키징 사양을 참조하십시오. http://www.microchip.com/packaging

권장되는 랜드 패턴

| 단위                       |      | 밀리미터     |      |      |

|--------------------------|------|----------|------|------|

| え                        | 수 한계 | MIN      | NOM  | MAX  |

| 접촉 피치 E                  |      | 0.40 BSC |      |      |

| 옵션 중앙 패드 너비              | X2   |          |      | 5.40 |

| 옵션 중앙 패드 길이              | Y2   |          |      | 5.40 |

| 접촉 패드 간격                 | C1   |          | 7.90 |      |

| 접촉 패드 간격                 | C2   |          | 7.90 |      |

| 접촉 패드 너비(Xnn)            | X1   |          |      | 0.20 |

| 접촉 패드 길이(Xnn)            | Y1   |          |      | 0.85 |

| 접촉 패드에서 중앙 패드까지의 거리(Xnn) | G1   | 0.83     |      |      |

| 접촉 패드 간 거리(Xnn)          | G2   | 0.20     |      |      |

| 열 비아 지름                  | V    |          | 0.30 |      |

| 열 비아 피치                  | EV   |          | 1.00 |      |

#### 참고:

1. 치수 및 공차는 ASME Y14.5M 참조

BSC: 기준 치수입니다. 공차를 제외하고 이론적으로 정확한 값으로 표시되었습니다.

2. 최상의 납땜 결과를 얻으려면 리플로우 공정 중 납 손실을 방지하기 위해 열 비아가 채워지거나 가려져야 합니다.

Microchip Technology Drawing C04-2479 Rev A

## APPENDIX A: 제품개요개정 내역

## 표 A-1: 개정 내역

| 개정                         | 섹션/그림/항목  | 수정 |

|----------------------------|-----------|----|

| DS0002819B(2021년 6월 4일)    | 공식 릴리즈    |    |

| DS00002819A(2018년 12월 10일) | 최초 문서 릴리즈 |    |

## MICROCHIP 웹 사이트

Microchip은 당사 WWW 사이트인 www.microchip.com을 통해 온라인 지원을 제공합니다. 이 웹 사이트는 고객이 파일과 정보를 쉽게 사용할 수 있도록 지원합니다. 즐겨 사용하는 인터넷 브라우저를 사용하여 액세스할 수 있으며 웹 사이트에는 다음 정보가 있습니다.

- 제품 지원 데이터 시트와 정오표, 애플리케이션 노트 및 샘플 프로그램, 설계 리소스, 사용자 가이드 및 하드웨어 지원 문서, 최신 소프트웨어 릴리스 및 보관된 소프트웨어

- 일반 지원 FAQ(자주 묻는 질문과 대답), 기술 지원 요청, 온라인 토론 그룹, Microchip 컨설턴트 프로그램 멤버 목로

- Microchip의 비즈니스 제품 선택 및 주문 가이드, 최신 Microchip 보도 자료, 세미나 및 이벤트 목록, Microchip 영업소 목록, 판매 대리점 및 공장 담당자

## 고객 변경 사항 알림 서비스

Microchip의 고객 알림 서비스는 고객에게 Microchip 제품에 대한 최신 정보를 제공합니다. 특정 제품군이나 관심 있는 개발 도구와 관련된 변경 사항, 업데이트, 수정 사항 또는 정오표가 있을 때마다 구독자에게 이메일 알림이 전송됩니다.

등록하려면 Microchip 웹 사이트(www.microchip.com)에 방문하십시오. "Support" 아래에서 "Customer Change Notification"을 클릭하고 등록 지침을 따릅니다.

### 고객 지원

Microchip 제품 사용자는 다음과 같이 여러 채널을 통해 지원을 받을 수 있습니다.

- 판매 대리점 또는 담당자

- 지역 영업소

- FAE(현장 애플리케이션 엔지니어)

- 기술 지원

고객은 해당 판매 대리점, 담당자 또는 FAE에게 지원을 문의해야 합니다. 지역 영업소에서도 고객을 지원할 수 있습니다. 영업소와 위치 목록은 이 문서 뒷면에 나와 있습니다.

다음 웹 사이트를 통해 기술 지원을 이용할 수 있습니다. http://www.microchip.com/support

## 제품 식별 시스템

주문 또는 제품 가격 및 배송과 같은 자세한 정보를 원하는 경우 공장 또는 기재된 영업소로 문의하십시오.

**디바이스:** LAN9370 = 5포트 스위치(1 RGMII/MII/RMII)

테이프 및 릴 옵션: 공백 = 표준 패키징(트레이)

T = 테이프 및 릴(Note 1)

**온도 범위:** -V = -40°C ~ +105°C(2등급 자동차)

**패키지:** KCX = 64핀 VQFN

**자동차 코드:** Vxx = "V" 접두사가 있는 3자리 문자 코드,

자동차 제품 지정

예:

a) LAN9370-V/KCXVAO 표준 패키징, 2등급 자동차 온도, 64핀 VQFN 패키지

b) LAN9370T-V/KCXVAO 테이프 및 릴, 2등급 자동차 온도, 64핀 VQFN 패키지

Note 1: 테이프 및 릴 식별자는 카탈로그 부품 번호 설명에만 표시됩니다. 이 식별자는 주문용 으로 사용되며 디바이스 패키지에 인쇄되 지 않습니다. 테이프 및 릴 옵션이 있는 패 키지 사용 가능 여부는 Microchip 영업소에

문의하십시오.

#### Microchip 디바이스의 코드 보호 기능에 대한 자세한 내용은 다음과 같습니다.

- Microchip 제품은 특정 Microchip 데이터 시트에 포함된 사양을 충족합니다.

- Microchip은 자사 제품군을 의도한 방식에 따라 정상 조건에서 사용할 경우 안전하다고 간주합니다.

- Microchip 디바이스의 코드 보호 기능을 훼손하려는 시도에 부정 및 심지어 불법적인 수단까지 이용되고 있습니다. 이러한 수단을 위해서는 Microchip 데이터 시트에 포함된 작동 사양을 벗어나는 방법으로 Microchip 제품을 사용하는 것으로 알고 있습니다. 이와 같이 코드 보호 기능을 훼손하려는 대부분의 시도는 Microchip의 지적 재산권을 위반하는 행위입니다.

- Microchip은 코드의 무결성에 대해 우려하는 고객과 협력하고자 합니다.

- Microchip 또는 다른 어떠한 반도체 제조업체도 자사의 코드 안전성을 보장할 수는 없습니다. 코드 보호는 Microchip이 제품의 "침해 불가능성"을 보증한다는 의미가 아닙니다. 코드 보호는 지속적으로 발전하고 있습니다. Microchip은 당사 제품의 코드 보호 기능을 지속적으로 개선하기 위해 노력하고 있습니다. Microchip의 코드 보호 기능을 훼손하려는 시도는 디지털 밀레니엄 저작권 법(Digital Millennium Copyright Act) 위반에 해당할 수 있습니다. 이러한 행위에 의해 귀하의 소프트웨어 또는 기타 저작권을 소유한 작업물에 무단 액세스가 이루어졌다면 해당 법률을 근거로 소송을 제기할 수 있습니다.

본 출판물에 포함된 정보는 Microchip 제품을 사용하여 설계하기 위한 목적으로만 제공됩니다. 디바이스 응용 프로그램 등과 관련하여 본 출판물에 포함된 정보는 고객의 편의를 위해 제공된 것이며 업데이트로 대체될 수 있습니다. 응용 프로그램이 해당 사양을 충족하는 지 확인하는 것은 고객의 책임입니다.

본 정보는 Microchip에서 제공한 "원본 그대로" 제공됩니다. Microchip은 조건, 품질 또는 성능과 관련된 특정 목적에 대한 비침해, 상품성 및 적합성을 포함하되 이에 국한되지 않는 정보와 관련하여 명시적, 묵시적, 서면, 구두, 법적 또는 다른 보증이나 진술을 하지 않습니다.

Microchip은 어떤 경우에도 정보 또는 정보 사용과 관련된 모든 종류의 간접적, 특수적, 징벌적, 부수적 또는 결과적 손실, 손상, 경비 또는 비용에 대해 책임을 지지 않습니다. Microchip의 사용 권고가 있었거나 손해에 대한 예측이 가능하더라도 이에 대해 책임지지 않습니다. 법에서 허용하는 범위까지, 정보 또는 정보 사용과 관련된 모든 청구에 대한 Microchip의 총 책임은 고객이 Microchip에 대해 직접 지불한 수수료(있는 경우)를 초과하지 않습니다. Microchip 디바이스를 생명 유지 및/또는 안전 용도로 사용할 경우 그로 인한 위험 부담은 전적으로 구매자에게 있으며, 구매자는 그러한 사용으로 인해 발생한 모든 손해, 청구, 소송 또는 비용으로부터 Microchip을 옹호, 보호하며 배상을 약속하는 데 동의합니다. 달리 명시하지 않는 한 Microchip 지적 재산권 하에 어떠한 라이선스도 묵시적 또는 다른 방식으로 제공되지 않습니다.

#### 상표

Microchip 이름과 로고, Microchip 로고, Adaptec, AnyRate, AVR, AVR 로고, AVR Freaks, BesTime, BitCloud, chipKIT, chipKIT 로고, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi 로고, MOST, MOST 로고, MPLAB, OptoLyzer, PackeTime, PIC, picoPower, PICSTART, PIC32 로고, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST 로고, SuperFlash, Symmetricom, SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron 및 XMEGA는 미국 및 기타 국가에서 Microchip Technology Incorporated의 등록 상표입니다.

AgileSwitch, APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, FlashTec, Hyper Speed Control, HyperLight Load, IntelliMOS, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus 로고, Quiet-Wire, SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider,, WinPath 및 ZL는 미국에서 Microchip Technology Incorporated의 등록 상 표입니다.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, Anyln, AnyOut, Augmented Switching, BlueSky, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, Espresso T1S, EtherGREEN, IdealBridge, In-Circuit Serial Programming, ICSP, INICnet, Intelligent Paralleling, Inter-Chip Connectivity, JitterBlocker, maxCrypto, maxView, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified 로고, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, RTAX, RTG4, SAM-ICE, Serial Quad I/O, simpleMAP, SimpliPHY, SmartBuffer, SMART-I.S., storClad, SQI, SuperSwitcher, SuperSwitcher II, Switchtec, SynchroPHY, Total Endurance, TSHARC, USBCheck, VariSense, VectorBlox, VeriPHY, ViewSpan, WiperLock, XpressConnect 및 ZENA는 미국과 기타 국가에서 Microchip Technology Incorporated의 상표입니다.

SQTP는 미국에서 Microchip Technology Incorporated의 서비스 마크입니다.

Adaptec 로고, Frequency on Demand, Silicon Storage Technology 및 Symmcom은 기타 국가에서 Microchip Technology Incorporated의 등록 상표입니다.

GestIC는 기타 국가에서 Microchip Technology Inc.의 자회사인 Microchip Technology Germany II GmbH & Co. KG의 등록 상표입니다.

본 자료에 언급된 그 외의 상표는 해당 기업의 재산입니다.

© 2023, Microchip Technology Incorporated, All Rights Reserved.

ISBN: 978-1-6683-2750-0

Microchip의 품질 관리 시스템에 대한 자세한 내용은 www.microchip.com/quality를 참조하십시오.

## 각국의 영업소 및 서비스

#### 미주

본사

2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277

기술 지원:

http://www.microchip.com/ support

웹 사이트:

www.microchip.com

애틀랜타

조지아주 덜루스 Tel: 678-957-9614 Fax: 678-957-1455

**텍사스주 오스틴** Tel: 512-257-3370

보스턴

매사추세츠주 웨스트버러 Tel: 774-760-0087 Fax: 774-760-0088

시카고

일리노이주 이타스카 Tel: 630-285-0071 Fax: 630-285-0075

댈러스

텍사스주 애디슨 Tel: 972-818-7423 Fax: 972-818-2924

**디트로이트** 미시간주 노바이 Tel: 248-848-4000

**텍사스주 휴스턴** Tel: 281-894-5983

**인디애나폴리스** 인디애나주 노블스빌 Tel: 317-773-8323

Fax: 317-773-5453 Tel: 317-536-2380

로스앤젤레스

캘리포니아주 미션비에이호

Tel: 949-462-9523 Fax: 949-462-9608 Tel: 951-273-7800 노스캐롤라이나주 롤리 Tel: 919-844-7510

뉴욕주 뉴욕 Tel: 631-435-6000

**캘리포니아주 새너제이** Tel: 408-735-9110 Tel: 408-436-4270

캐나다 - 토론토 Tel: 905-695-1980 Fax: 905-695-2078 아시아/태평양

호주 - 시드니 Tel: 61-2-9868-6733

중국 - 베이징 Tel: 86-10-8569-7000

중국 - 청두 Tel: 86-28-8665-5511

중국 - 충칭 Tel: 86-23-8980-9588

중국 **- 둥관** Tel: 86-769-8702-9880

중국 - 광저우 Tel: 86-20-8755-8029

중국 - 항저우 Tel: 86-571-8792-8115

중국 - 홍콩 SAR Tel: 852-2943-5100

중국 - 난징

Tel: 86-25-8473-2460 중국 - 칭다오

Tel: 86-532-8502-7355

중국 - 상하이 Tel: 86-21-3326-8000

중국 **- 선양** Tel: 86-24-2334-2829

중국 - 선전 Tel: 86-755-8864-2200

중국 - 쑤저우 Tel: 86-186-6233-1526

중국 - 우한 Tel: 86-27-5980-5300

중국 - 시안 Tel: 86-29-8833-7252

중국 - 샤먼 Tel: 86-592-2388138

중국 **- 주하이** Tel: 86-756-3210040 아시아/태평양

인도 - 벵갈루루 Tel: 91-80-3090-4444

인도 - 뉴델리 Tel: 91-11-4160-8631

**인도 - 푸네** Tel: 91-20-4121-0141

일본 - 오사카 Tel: 81-6-6152-7160

<mark>일본 - 도쿄</mark> Tel: 81-3-6880-3770

한국 - 대구

Tel: 82-53-744-4301 한국 - 서울

말레이시아 - 쿠알라룸푸르

Tel: 60-3-7651-7906 말레이시아 - 페낭

Tel: 82-2-554-7200

Tel: 60-4-227-8870

**필리핀 - 마닐라** Tel: 63-2-634-9065

**싱가포르** Tel: 65-6334-8870

**대만 - 신주** Tel: 886-3-577-8366

대만 **- 가오슝** Tel: 886-7-213-7830

대만 - 타이베이 Tel: 886-2-2508-8600

태국 - 방콕 Tel: 66-2-694-1351

베트남 - 호치민 Tel: 84-28-5448-2100 유럽

오스트리아 - 벨스 Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

덴마크 - 코펜하겐 Tel: 45-4485-5910 Fax: 45-4485-2829

**핀란드 - 에스포** Tel: 358-9-4520-820

프랑스 - 파리 Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**독일 - 가르힝** Tel: 49-8931-9700

독일 - 하안 Tel: 49-2129-3766400

**독일 - 하일브론** Tel: 49-7131-72400

독일 - 카를스루에 Tel: 49-721-625370

독일 - 뮌헨 Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**독일 - 로젠하임** Tel: 49-8031-354-560

**이스라엘 - 라아나나** Tel: 972-9-744-7705

**이탈리아 - 밀라노** Tel: 39-0331-742611 Fax: 39-0331-466781

**이탈리아 - 파도바** Tel: 39-049-7625286

네덜란드 - 드루넨 Tel: 31-416-690399 Fax: 31-416-690340

노르웨이 - 트론헤임 Tel: 47-7288-4388

**폴란드 - 바르샤바** Tel: 48-22-3325737

루마니아 - 부쿠레슈티 Tel: 40-21-407-87-50

스페인 - 마드리드 Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**스웨덴 - 예테보리** Tel: 46-31-704-60-40

**스웨덴 - 스톡홀름** Tel: 46-8-5090-4654

영국 - 오킹엄 Tel: 44-118-921-5800 Fax: 44-118-921-5820